awawa's report: 電子工作、その他趣味についての記録日記ブログです。

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

AtMega168データシート翻訳

http://awawa.hariko.com/chira-ura/index.html

24章 debugWIRE オンチップ・デバッグシステム

最初の翻訳を完了しました。

http://awawa.hariko.com/chira-ura/atmega168-chapter24-jp.html

この章は非常に短く、いくつかの注意事項以外は特に注目すべき内容もないので、さらっと流して次へ行きたいと思います。

debugWIREはリセット端子を使用して1-wireでデバッグ機能を提供する機能です。

ピン数の少ないデバイスではJTAGなどのデバッグ機能の代替として提供されているようです。

今回は、debugWIREをつかえる機器をもっていないので試すことができませんでした。

制限事項(24.5)にあるとおり、

肝心のdebugWIREプロトコルについては一切の記述がないので、「注意事項」としてのみ存在する章といえます。

以降、いよいよメモリプログラミングに関する章に突入です。

ではまた。

http://awawa.hariko.com/chira-ura/index.html

24章 debugWIRE オンチップ・デバッグシステム

最初の翻訳を完了しました。

http://awawa.hariko.com/chira-ura/atmega168-chapter24-jp.html

この章は非常に短く、いくつかの注意事項以外は特に注目すべき内容もないので、さらっと流して次へ行きたいと思います。

debugWIREはリセット端子を使用して1-wireでデバッグ機能を提供する機能です。

ピン数の少ないデバイスではJTAGなどのデバッグ機能の代替として提供されているようです。

今回は、debugWIREをつかえる機器をもっていないので試すことができませんでした。

制限事項(24.5)にあるとおり、

- RESET端子を本来の機能(リセット)に使用できなくなる

- SPIへのクロック供給を止めてはいけない(PRRレジスタのPRSPIビットに注意)

- スリープモードでも一部の周辺回路が動作を継続してしまう

肝心のdebugWIREプロトコルについては一切の記述がないので、「注意事項」としてのみ存在する章といえます。

以降、いよいよメモリプログラミングに関する章に突入です。

ではまた。

PR

ATmega48/88/168 データシート翻訳

http://awawa.hariko.com/chira-ura/index.html

「23章 A/Dコンバータ(ADC)」 粗訳を完了しました。

久しぶりの更新で、いろいろ忘れていることがあって時間がかかってしまいました(汗)。

ATmega168のA/Dコンバータは逐次変換方式で、プリスケーラを通してクロック供給が必要です。

変換時間がCPUの動作に比べると長時間となるため、動作開始タイミングと結果の参照タイミングが制御関連のアプリケーションでは重要になってきます。

この章は、動作タイミングとそれを生成するロジックを重点的に解説した内容となっていて、ADC各レジスタの設定内容を深く理解することができると思います。特に、自動トリガの要因として「割り込みフラグ」を利用している構造が面白いところです。

ADCの変換開始のタイミング生成手段として、

「ハードウェアのトリガ要因」としては、外部割込み、アナログ・コンパレータ、タイマー0/1のイベントが使用できます。アナログ系の制御や、一定時間間隔でのアナログ・データ取得を意識した設計のようです。

変換完了の方も、

面白いのは、トリガ要因としては「A/D変換完了割り込みフラグ」を指定でき、これを指定すると、ハードウェア的に「無限ループ」を形成して、ADCのプリスケーラで決まるタイミングでCPU側と関係なく変換動作を続けるモード(フリーラン・モード)になります。一定時間間隔の計測には便利そうです。

さて、いよいよ周辺機能もこれで終了となりました。

後残す大物はメモリ関連(自己書き換え、ISP、ブートローダーなど)です。

英語の話:

この章にちょっと面白い表現がありました。

(抜粋)

日常的な単語解釈だと、

では。

http://awawa.hariko.com/chira-ura/index.html

「23章 A/Dコンバータ(ADC)」 粗訳を完了しました。

久しぶりの更新で、いろいろ忘れていることがあって時間がかかってしまいました(汗)。

ATmega168のA/Dコンバータは逐次変換方式で、プリスケーラを通してクロック供給が必要です。

変換時間がCPUの動作に比べると長時間となるため、動作開始タイミングと結果の参照タイミングが制御関連のアプリケーションでは重要になってきます。

この章は、動作タイミングとそれを生成するロジックを重点的に解説した内容となっていて、ADC各レジスタの設定内容を深く理解することができると思います。特に、自動トリガの要因として「割り込みフラグ」を利用している構造が面白いところです。

ADCの変換開始のタイミング生成手段として、

- ソフトウェアでビットをセットしたらすぐ開始。

- ハードウェアのトリガ要因で開始。それまで待機。

「ハードウェアのトリガ要因」としては、外部割込み、アナログ・コンパレータ、タイマー0/1のイベントが使用できます。アナログ系の制御や、一定時間間隔でのアナログ・データ取得を意識した設計のようです。

変換完了の方も、

- ソフトウェアでビットを監視して完了を待つ

- ADC変換完了割り込みを利用する

面白いのは、トリガ要因としては「A/D変換完了割り込みフラグ」を指定でき、これを指定すると、ハードウェア的に「無限ループ」を形成して、ADCのプリスケーラで決まるタイミングでCPU側と関係なく変換動作を続けるモード(フリーラン・モード)になります。一定時間間隔の計測には便利そうです。

さて、いよいよ周辺機能もこれで終了となりました。

後残す大物はメモリ関連(自己書き換え、ISP、ブートローダーなど)です。

英語の話:

この章にちょっと面白い表現がありました。

(抜粋)

p.249 23.5.2 ADC Voltage Reference より:

Single ended channels that exceed VREF will result in codes close to 0x3FF.

日常的な単語解釈だと、

「・・・VREFを超える入力は0x3FFに近い値に変換されます」

となるのですが、ADCの精度が10ビット=0x3FFであることを考えるとラスト数ビットはふらふら落ち着かないような印象を受け、ちょっと設計者にとっては困った内容です。

誤記にしては軽率すぎるので、いろいろ調べたところ、数学(トポロジー)的なニュアンス「近傍」を含んでいるようです。

(Wikipediaより引用、[http://en.wikipedia.org/wiki/Closeness_(mathematics)#Definition])

Similarly a set B is called close to a set A if

(引用ここまで)

の"close"が意味するところが近いように思います。

要するに、「VREFを超えるアナログ電圧(実数)点全て集合」が「ただ一つの点"0x3FF"で構成される集合」に射影される、ということが書かれているというわけでしょうか。ちょっと考えすぎのような気もしますが、どうも英語の形容詞"close"には、「接近している」ということの他に、「閉じ込められている」動詞のニュアンス"closed"があるのかもしれません。(もしくは、原文執筆が英語ではなかったのかも)

となるのですが、ADCの精度が10ビット=0x3FFであることを考えるとラスト数ビットはふらふら落ち着かないような印象を受け、ちょっと設計者にとっては困った内容です。

誤記にしては軽率すぎるので、いろいろ調べたところ、数学(トポロジー)的なニュアンス「近傍」を含んでいるようです。

(Wikipediaより引用、[http://en.wikipedia.org/wiki/Closeness_(mathematics)#Definition])

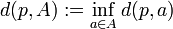

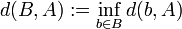

Given a metric space (X,d) a point p is called close or near to a set A if

d(p, A) = 0,

where the distance between a point and a set is defined as

Similarly a set B is called close to a set A if

d(B, A) = 0

where

(引用ここまで)

の"close"が意味するところが近いように思います。

要するに、「VREFを超えるアナログ電圧(実数)点全て集合」が「ただ一つの点"0x3FF"で構成される集合」に射影される、ということが書かれているというわけでしょうか。ちょっと考えすぎのような気もしますが、どうも英語の形容詞"close"には、「接近している」ということの他に、「閉じ込められている」動詞のニュアンス"closed"があるのかもしれません。(もしくは、原文執筆が英語ではなかったのかも)

まあ、数学的に仰々しいことを書く箇所でもないので、今回は、

「・・・VREFを超える入力は全て同一の値0x3FFに変換されます」

と軽くしておきました。

「・・・VREFを超える入力は全て同一の値0x3FFに変換されます」

と軽くしておきました。

では。

ATmega48/88/168 データシート 21. TWI 粗訳完了

http://awawa.hariko.com/chira-ura/index.html

ようやく、2線式シリアル・インターフェース、TWIの粗訳が完了しました。

大人の事情でTWIと名づけられていますが、フィリップス(現NXP)互換のI2Cインターフェースです。

この章は、半分近くをI2Cの動作原理の説明に費やしており、非常に長いものとなっています。

しかしながら、とてもわかりやすい説明ですので、I2Cの基礎から理解したい方々には良い資料になると思います。

ひとつひとつの状態を丁寧に説明してあるので、私も勉強になりました。

さて、データシートからみると、AVRのTWI(I2C)は、ほぼ裸に近いハードウェアをコントロールするような構成になっています。

柔軟性があるともいえますが、なにかステータス変更がある度に割り込みが発生するので、ちょっと面倒くさいような印象も受けます。

とはいっても、

マスター1個とスレーブ1個(シリアルEEPROMの接続など)だけ、とか、スレーブ専用(他のMCUの周辺ICとして動かす)とか、シンプルな用途で使う場合、可能性のあるステートの処理だけを組み込んで、全ての状態を網羅したステート・マシンを作る必要はないので、それほど苦労するものではないかもしれません。

ともかくも、これを読んでI2Cを使ってみたくなり、現在簡単な実験回路を考案中です。

さて、この章には巨大なステート遷移図があり、図中に説明文が詰め込まれていますが、今のところ英語のままになっています。

図の翻訳は、これまでの他の章ではスキップしてますが、さすがにここは翻訳しないとせっかくの資料が役に立たないので、現在、進行中です。

では。

http://awawa.hariko.com/chira-ura/index.html

ようやく、2線式シリアル・インターフェース、TWIの粗訳が完了しました。

大人の事情でTWIと名づけられていますが、フィリップス(現NXP)互換のI2Cインターフェースです。

この章は、半分近くをI2Cの動作原理の説明に費やしており、非常に長いものとなっています。

しかしながら、とてもわかりやすい説明ですので、I2Cの基礎から理解したい方々には良い資料になると思います。

ひとつひとつの状態を丁寧に説明してあるので、私も勉強になりました。

さて、データシートからみると、AVRのTWI(I2C)は、ほぼ裸に近いハードウェアをコントロールするような構成になっています。

柔軟性があるともいえますが、なにかステータス変更がある度に割り込みが発生するので、ちょっと面倒くさいような印象も受けます。

とはいっても、

マスター1個とスレーブ1個(シリアルEEPROMの接続など)だけ、とか、スレーブ専用(他のMCUの周辺ICとして動かす)とか、シンプルな用途で使う場合、可能性のあるステートの処理だけを組み込んで、全ての状態を網羅したステート・マシンを作る必要はないので、それほど苦労するものではないかもしれません。

ともかくも、これを読んでI2Cを使ってみたくなり、現在簡単な実験回路を考案中です。

さて、この章には巨大なステート遷移図があり、図中に説明文が詰め込まれていますが、今のところ英語のままになっています。

図の翻訳は、これまでの他の章ではスキップしてますが、さすがにここは翻訳しないとせっかくの資料が役に立たないので、現在、進行中です。

では。

ATmega48/88/168 データシート翻訳

19. USART0 粗訳完了

http://awawa.hariko.com/chira-ura/index.html

後回しにしていた19. USART0を完了しました。

今までで一番長い章で、結構時間がかかりましたが、内容は比較的ストレートなAVRのUSART解説なので、技術的には、それほど難解な場所はありません。むしろ、USARTの構造や動作を勉強するのに役立つのではないかと思います。(自分にとって、勉強になりました)

なかなか秀逸な解説は、「クロック・リカバリ」、「データ・リカバリ」の部分で、非同期通信の基本動作を理解することができます。

今回、翻訳を進めながら、同時にSPI、USARTの実験をしていたのですが、やはり動くものがそばにあると理解が深まります。別の機会にかけたら、と思います。

さて、次回は中盤の山TWIにとりかかります。

これも色々と勉強になることが多いことを期待しています。

英語の話、というかメモ:

19. USART0 粗訳完了

http://awawa.hariko.com/chira-ura/index.html

後回しにしていた19. USART0を完了しました。

今までで一番長い章で、結構時間がかかりましたが、内容は比較的ストレートなAVRのUSART解説なので、技術的には、それほど難解な場所はありません。むしろ、USARTの構造や動作を勉強するのに役立つのではないかと思います。(自分にとって、勉強になりました)

なかなか秀逸な解説は、「クロック・リカバリ」、「データ・リカバリ」の部分で、非同期通信の基本動作を理解することができます。

- ボーレート・クロックに多少の誤差があっても、正しく受信できる仕組み

- どこまでの誤差が許容されるか、の予測と設計

- 倍速モードのメリットとデメリット

今回、翻訳を進めながら、同時にSPI、USARTの実験をしていたのですが、やはり動くものがそばにあると理解が深まります。別の機会にかけたら、と思います。

さて、次回は中盤の山TWIにとりかかります。

これも色々と勉強になることが多いことを期待しています。

英語の話、というかメモ:

- "clock/data recovery"

"recovery"を「リカバリ」とするか、「復元」とするか迷いました。「クロック・リカバリ」は比較的ハード用語として定着しているように思いますが、「データ・リカバリ」と書くと、どちらかというとハードディスクやOSの復旧のことのようなイメージがありました。

今回は、結局、「リカバリ」で統一。

今回は、結局、「リカバリ」で統一。

- "metastable"

直訳すると「準安定状態」。化学では頻出用語で、反応進行中の途中状態を表しますが、USARTの場合、"metastable"状態と"stable"状態とが交互に現れる、というニュアンスを出しているのでしょうか。めんどくさいので「不安定な状態」とだけ。

ATmega48/88/168 データシート翻訳

20. USART SPIモード 粗訳完了

http://awawa.hariko.com/chira-ura/index.html

19.USART0をスキップして、先に20章を翻訳。

あまり深い理由は無いけれど、なんとなく同じSPIを先にやった方が効率良さそうな気がしたので、19章をスキップしました。次は、19章の予定。

USART SPIモードとSPIの違いについては、20.7節によくまとまっています。

なぜ、こんなモードがあるのか、ちょっと不思議ですが、SPIを2系統使いたいときなどには良いのかも知れませんね。

英語の話:

SPIの"leading/trailing edge"のところで、シフト・レジスタの"sampling/setup"というのがあったのですが、この章にヒントがあって、次の訳語に変更しました。

では、今度こそ19章へつづく。

20. USART SPIモード 粗訳完了

http://awawa.hariko.com/chira-ura/index.html

19.USART0をスキップして、先に20章を翻訳。

あまり深い理由は無いけれど、なんとなく同じSPIを先にやった方が効率良さそうな気がしたので、19章をスキップしました。次は、19章の予定。

USART SPIモードとSPIの違いについては、20.7節によくまとまっています。

- USART SPI > SPIな点

- 送信器が二重バッファ構造(USART SPI)

- USART SPIの方が受信器のバッファが深い

- USART SPI < SPIな点

- 書き込み衝突ビット(WCOL)はSPIのみ

- USART SPIはマスター動作のみ対応

- 倍速モードはSPIのみ

- 割込みタイミングが非互換

- 当然ながら、端子が違う

なぜ、こんなモードがあるのか、ちょっと不思議ですが、SPIを2系統使いたいときなどには良いのかも知れませんね。

英語の話:

SPIの"leading/trailing edge"のところで、シフト・レジスタの"sampling/setup"というのがあったのですが、この章にヒントがあって、次の訳語に変更しました。

- sampling = 「ラッチ動作」

- setup = 「シフト動作」

では、今度こそ19章へつづく。

カレンダー

| 03 | 2026/04 | 05 |

| S | M | T | W | T | F | S |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 |

フリーエリア

最新記事

(05/04)

(04/16)

(03/31)

(01/29)

(10/23)

最新トラックバック

ブログ内検索

最古記事

(02/23)

(02/24)

(03/08)

(03/18)

(06/24)

P R